one of the method is , using LFSR, LFSR generates random stimulus and it is expected that chip is in its normal functional mode. with the configuration, with LFSR , one can validate the data path in system or in IP.

What is the motivation for BIST ?

-> cost-efficient testing

-> stuck-at-fault model

-> cost of ATE (Automatic Test Equipment)

Types of BIST

-> on-line BIST

-> Concurrent on-line BIST

Occurs simultaneously with normal functional operation , normally coding techniques or duplication and comparison are used.

-> Non-concurrent on-line BIST

Carried out while in idle state , by executing software or firmware routines .

-> off-line BIST

System is not in its normal functional mode.

-> Functional off-line BIST

It is based on a functional description of the circuit under test and uses functional high level fault models.

-> Structural off-line BIST

Execution based on the structure of the circuit under test and used structural fault models.

Example - Stuck-At-Fault (SAF) - cell stuck at constant value

Transition Fault (TF) - a cell which fails to go from 0->1 or 1->0 transition

Coupling Fault (CF) - write operation to one cell changes the contents of a second cell

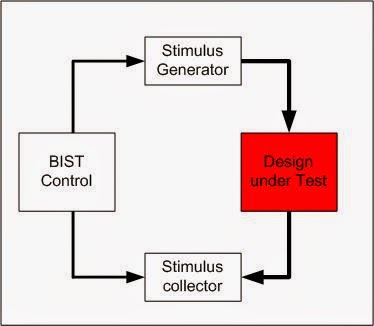

General Architecture of BIST

Below is typical architecture of BIST testing , bist generator and bist collector would be inside DUT or outside DUT , depends on the BIST type.

LFSR Based Testing :

LFSR : Linear Feedback Shift Register , hardware that generates psedo-random pattern for CUT (circuit under test)

BILBO : Built-In logic block observer , extra hardware need to convert flip-flop into scan chain in test mode.

Exhaustive Testing : Apply all possible 2 (power of) n pattern to a circuit with n inputs , this will take more ATE time.

Pseudo-exhaustive testing: Break circuit into small , overlapping blocks and test it.

Psudo Random test generation :

PRBS is basically a polynomial having a standard definition, for exam - PRBS7, PRBS8, PRBS10, PRBS 31 ..

higher the number of PRBS, pattern will be more random and possibilities to hit a expected pattern in pattern generation will increased.

below is one example of implementation of polynomial, if you are more interested to go in more deep, send a email to me.

Ref -

http://en.wikipedia.org/wiki/Built-in_self-test

http://www.asic.co.in/ppt/BIST2.pdf

No comments:

Post a Comment