Q1. what are the basic components of a module ? which component are mandatory ?

In hardware design (such as in Verilog, VHDL, or FPGA design), a module typically refers to a self-contained unit that encapsulates a set of functionality or behavior. Modules are often used to represent components of a design, such as a flip-flop, ALU, counter, or memory unit.

Basic Components of a Module:

A module can be made up of several key components, which can vary depending on the complexity of the design. The typical components include:

-

Module Declaration:

- This is the definition of the module, which includes the module's name and its input/output ports.

- Example in Verilog:

module my_module (input wire a, input wire b, output wire sum);

-

Inputs and Outputs:

- Inputs: These are signals that come from other modules or external components and are used inside the module for operations.

- Outputs: These are signals that are generated by the module and are sent to other modules or external components.

- Example:

input wire clk, reset; output reg [7:0] data_out;

-

Internal Signals (Wires, Registers):

- These are variables used inside the module to store intermediate values or results.

- Wires: Represent continuous signals, usually connected to other modules or logic.

- Registers (Regs): Store values that can change on clock edges (for sequential logic).

- Example:

wire [3:0] temp; reg [7:0] counter;

-

Behavioral Description:

- This section describes how the module behaves based on the inputs and internal signals. It can be expressed through combinational logic, sequential logic, or a mix of both.

- Example:

always @(posedge clk or posedge reset) begin if (reset) counter <= 8'b0; else counter <= counter + 1; end

-

Instantiation of Other Modules (if applicable):

- A module can instantiate other sub-modules inside it to create more complex systems.

- Example:

submodule1 inst1 (.input1(a), .output1(temp));

-

Endmodule:

- This marks the end of the module definition.

- Example:

endmodule

Mandatory Components in a Module:

While a module can have many optional components, the following are mandatory for any functional module:

-

Module Declaration:

The module must be declared with themodulekeyword, followed by the module's name and its input/output ports (or an empty list if there are no ports).- Mandatory: A module needs at least one input or output port, even if the functionality is trivial.

-

Input and Output Ports:

- At least one input or output port is mandatory for a module, as this is the interface to the external environment (or to other modules).

In a simple module that does nothing, you can have a module with no functionality but still have input/output ports:

module my_module (input wire clk, output wire out); endmodule -

Behavioral or Structural Definition:

- Even if the module just holds wires or registers, there must be some sort of behavioral description (like always blocks for sequential logic) or structural description (using instantiated sub-modules).

-

Endmodule:

- Every Verilog module must end with the

endmodulekeyword to mark the end of the module's scope.

- Every Verilog module must end with the

Optional Components:

-

Internal Signals: Not all modules need internal signals. For simple combinational modules, internal registers or wires may be unnecessary.

-

Instantiation of Submodules: A module doesn't necessarily have to instantiate other submodules. A simple module can be self-contained without using other modules.

-

Parameter Declaration: While parameters can be defined for flexibility, they are not mandatory. Parameters are used to define constant values that can be configured during instantiation of the module.

Example of a Simple Module:

Here's a simple Verilog module example with basic mandatory components:

module simple_adder (input wire a, input wire b, output wire sum);

// Combinational logic to sum inputs

assign sum = a + b; // This is a simple addition

endmodule

In this case:

- The module declaration defines the name (

simple_adder) and the input/output ports (a,b,sum). - The behavioral description defines the logic for the module (in this case, a simple addition).

- The endmodule marks the end of the module.

Summary:

- Mandatory components of a module:

- Module Declaration (

module <name> (...)) - Inputs/Outputs (at least one)

- Behavioral/Structural Description

- Endmodule

- Module Declaration (

Optional components like internal signals, submodule instantiation, and parameters are used depending on the complexity of the design but are not strictly mandatory for a basic module.

Q2 Does a module that does not interact with its environment have any I/O ports ? does it have a port list in the module definition ?

A module which does not interact with its environment , will not have any I/O ports , hence port list will not be required. One of the example is , when you create the testbench , the top level testbench doe not have any port as it just contain the DUT and other component.

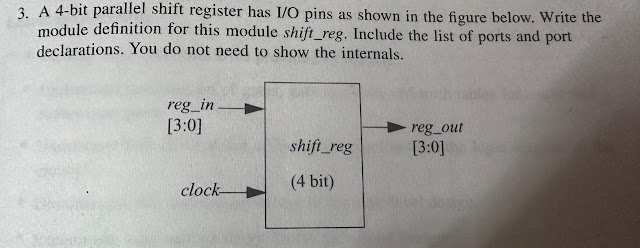

Q3 A 4-bit parallel shift register has IO pins as shown in figure below. Write the module definition for this module shift_reg. Include the list of ports and port declaration.

Here is the module definition:

module shift_reg (

input [3:0] reg_in,

input clock ,

output reg [3:0] reg_out

) ;

--

--

endmodule

Q4. declare a top level module name stimulus. Define REG_IN (4-bit) and CLK (1 bit ) as reg register variables and REG_OUT (4-bit) as wire. Instantiate the module shift_reg and call it sr1. Connect the ports by ordered list.

Answer :

module stimulus ;

reg [3:0] reg_in ; \\ verilog is case insensitive language , so REG_IN and reg_in would be interpreted same by the compiler.

reg clk ;

reg [3:0] reg_out ;

shift_reg sr1 ( reg_in , clk , reg_out ) ; //assuming the port declaration in shift_reg module is same as here.

endmodule

Here is the more detailed explanation between named connection and ordered connections.

In Verilog, module instantiation refers to creating an instance of a module within another module. When instantiating a module, you can connect the ports of the instantiated module using either named connections or ordered connections.

In ordered connections, the order of the ports in the instantiation must match the order of the ports in the module declaration. This method is less flexible than named connections because the order of the ports must be strictly followed.

Example: Instantiating a shift_reg module using ordered connections.

Let's consider we have the shift_reg module from the previous example, which has the following ports:

clk(input)reset(input)shift(input)data_in(input, 4-bit)data_out(output, 4-bit)

Now, we will instantiate this shift_reg module inside another module using ordered port connections.

Verilog Code:

module top_module(

input wire clk, // Clock signal

input wire reset, // Reset signal

input wire shift, // Shift control signal

input wire [3:0] data_in, // 4-bit input data

output wire [3:0] data_out // 4-bit parallel output data

);

// Instantiating the shift_reg module using ordered connections

shift_reg u_shift_reg (

clk, // Connect to shift_reg's clk

reset, // Connect to shift_reg's reset

shift, // Connect to shift_reg's shift

data_in, // Connect to shift_reg's data_in

data_out // Connect to shift_reg's data_out

);

endmodule

Explanation:

-

Top Module:

- The

top_moduledefines the ports:clk,reset,shift,data_in, anddata_out. - These signals are intended to be connected to a

shift_regmodule.

- The

-

Module Instantiation (

shift_reg u_shift_reg):- Inside

top_module, theshift_regmodule is instantiated with the instance nameu_shift_reg. - The ports of the

shift_regmodule are connected in the order they were declared. This is ordered connection.- The first port

clkoftop_moduleis connected to the first portclkofshift_reg. - The second port

resetoftop_moduleis connected to the second portresetofshift_reg. - The third port

shiftoftop_moduleis connected to the third portshiftofshift_reg. - The fourth port

data_inoftop_moduleis connected to the fourth portdata_inofshift_reg. - The fifth port

data_outoftop_moduleis connected to the fifth portdata_outofshift_reg.

- The first port

- Inside

Key Points:

- Ordered connections require that the ports are connected in the exact same order as they are declared in the module definition.

- This is a simple and compact way of instantiating a module but requires strict attention to the order of the ports.

This method is especially useful in small designs or when the port order in the module is unlikely to change. However, in larger designs, named connections (where you explicitly name each port in the instantiation) are generally preferred because they are more readable and maintainable.

Q5 . connect the port in step 4 by name.

here , module stimulus is same but when instantiating the shift_reg , connections would be using the name.

shift_reg sr1 ( .reg_in (reg_in),

.clk (clk ),

.reg_out (reg_out ) );

Q6 write the hier name for clk , reg_in and reg_out.

reg_in -> sr1.reg_in

clk -> sr1.clk

reg_out sr1.reg_out

Q7 -> its almost same as question 6 - > put your answer in comment.

No comments:

Post a Comment